### Realization of resistorless floating inductor using modified CDTA

Dinesh Prasad\*, Zainab Haseeb, Mainuddin & Md W Akram

Department of Electronics and Communication Engineering, Faculty of Engineering and Technology, Jamia Millia Islamia, New Delhi 110 025, India

Received 25 May 2017; accepted 10 August 2018

This paper briefly introduces a modified current differencing *trans*-conductance amplifier (M-CDTA) and its application in the simple realization of floating inductors. The proposed inductor is positive floating and lossless type offering the advantage of wider frequency bandwidth. The resulting equivalent inductance has been realized using one M-CDTA and one grounded capacitor and its inductance value can be adjusted electronically by proper tuning of the bias current. Results demonstrating the behavior of the circuit and its application confirming the theoretical analysis are verified through PSPICE simulations.

Keywords: M-CDTA, Electronically adjustable, Floating inductor, Resistorless, Grounded capacitor

### 1 Introduction

During the last two decade much effort has been applied in the realization of inductor as it is one of the very important element in the design of filter and oscillator. The large size of the available coil inductor makes it impossible to fabricate on chip. Floating inductor simulator circuit offering high performance has been excavated and reported several times in the literature with a possible reason the emerging application<sup>1-9</sup>. The current-mode circuits have become a topic of keen interest because of their potential advantage in, simple circuitry, better linearity, reduced power consumption and increased dynamic range<sup>10,11</sup>. The circuit introduced in this paper offers considerable advantages such as compact structure, and a circuit design which is resistorless.

CDTA is a 5-terminal current mode active element<sup>12</sup>, and it is found to be a versatile element in the realization of filters used in analog signal processing circuits. It offers wider frequency bandwidth and it is free from parasitic input capacitances.

This paper aims to introduce a modified version of CDTA and its application in the realization of inductor. The proposed lossless inductor is resistorless and it is electronically tunable by adjusting the bias current.

### 2 Circuit Configuration

### 2.1 Basic concept of M-CDTA

The proposed M-CDTA is similar to that of conventional CDTA with the exception of an OTA

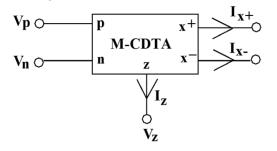

From the basic operation of ideal M-CDTA, the relationship between its terminals can be characterized by the help of following matrix:

$$\begin{bmatrix} I_z \\ I_{x_+} \\ I_{x_-} \end{bmatrix} = \begin{bmatrix} 0 & g_{m1} & -g_{m1} \\ g_{m2} & 0 & 0 \\ -g_{m2} & 0 & 0 \end{bmatrix} \begin{bmatrix} V_z \\ V_p \\ V_n \end{bmatrix} \qquad \dots (1)$$

where  $g_{m1}$  and  $g_{m2}$  are the *trans*-conductance gain of OTA and CDTA, respectively. Here  $g_m$  depends on external DC bias current, and hence the proposed configuration is electronically tunable.

## 2.2 Inductance simulator using M-CDTA and a grounded capacitor

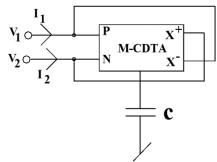

A positive lossless floating inductor can be realized by the help of one M-CDTA and a grounded capacitor as shown in Fig. 2

Analyzing the proposed floating inductor yielded the following relation:

Fig. 1 – Symbol of M-CDTA.

preceding CDTA offering non-zero input voltage at the p and n input terminals, respectively. The symbol of M-CDTA is illustrated in Fig. 1.

<sup>\*</sup>Corresponding author (E-mail: dprasad@jmi.ac.in)

$$\begin{bmatrix} I_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} Y_{eq} \end{bmatrix} \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix} \qquad \dots (2)$$

$$Y_{eq} = \left(\frac{2g_{m1} g_{m2}}{sc}\right) \qquad ...(3)$$

$$Z_{eq} = \frac{1}{Y_{eq}} = S\left(\frac{C}{2g_{m1}g_{m2}}\right)$$

...(3.1)

$$Z_{eq} = sL_{eq} \qquad ...(3.2)$$

Where C is a grounded capacitor. It is very much evident from Eq. (3) that the equivalent value of the realized floating inductance is found to be:

$$L_{eq} = \frac{c}{2g_{m1} g_{m2}} \qquad ...(4)$$

Obviously  $L_{eq}$  is electronically tunable, lossless and resistorless.

The floating inductor circuit realized in Fig. 2 is using the following components: C=1 nF,  $g_{\rm m}=g_{\rm m1}=g_{\rm m2}=427.599 \,\mu\text{A}/\text{V}$ , which results in  $L_{\rm eq}=2.73$  mH.

### 3 Applications

# 3.1 Application of floating inductance simulator as a band pass filter

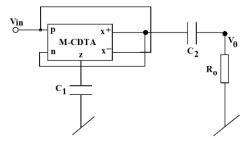

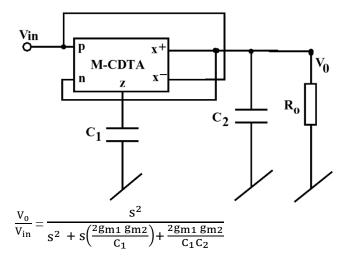

Application of the proposed floating inductor in Fig. 2 can be demonstrated by employing in a RLC band pass filter as shown in Fig. 3.

The transfer function obtained from Fig. 3 is given as:

$$\frac{V_0}{V_{in}} = \frac{S(\frac{2Rg_{m_1}g_{m_2}}{C})}{S^2 + S(\frac{2Rg_{m_1}g_{m_2}}{C}) + \frac{2g_{m_1}g_{m_2}}{C^2}}$$

Fig. 2 – Inductance simulator.

Fig. 3 – BPF based on inductor simulated using M-CDTA.

... (2)

$$\omega_0 = \frac{1}{C} \sqrt{2g_{m1}g_{m2}}$$

...(3)

$$Q_0 = \frac{\omega_0 \ C}{2Rg_m^2}$$

...(3.1)

$$f_0 = \frac{1}{2\pi C} \sqrt{2g_{m1}g_{m2}}$$

The components specifications used are C=1 nF, R=2.338 k $\Omega$ ,  $g_{m1}=g_{m2}=427.99$   $\mu$ A/V, it is observed that the frequency was found to be 96.3 KHz.

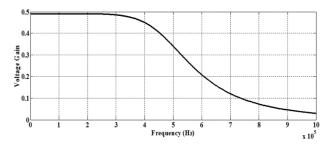

# 3.2 Application of floating inductance simulator as normalized fourth order butterworth LPF

To demonstrate the application of the proposed floating inductor in Fig. 2, it is also employed in a normalized fourth order butterworth LPF as shown in Fig. 4.

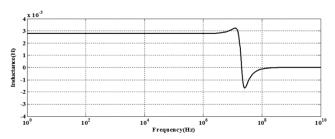

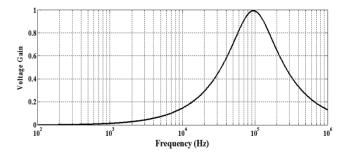

#### 4 Simulation Results

The theoretical predictions of the proposed inductance simulator, the band pass filter and fourth order butterworth LPF employing M-CDTA have been verified in this section using PSPICE program and are shown in Fig. 5, Fig. 6 and Fig. 7, respectively. The CDTA was realized using 0.50- $\mu$ m CMOS technology. For all inductor and filter response value of capacitor is taken as 1 nF and *trans*-conductance gain is set around 427.599  $\mu$ A/V (which is obtained from OTA structure<sup>26</sup> of Fig. 4). Extremely little deviation is observed in the ideal and the simulated value of inductor as well as the cut-off frequency of band pass filter.  $L_{eq}$  (simulated)

Fig. 4 – Normalized fourth order Butterworth LPF.

Fig. 5 – Frequency response of the simulated floating inductor.

= 2.789 mH and  $f_0$  (simulated) = 95.641 kH. The comparison of the proposed circuit with other published work is shown in Table 1.

The transfer function obtained from Fig. (8) is given as:

Fig. 6 – Frequency response of BPF using the simulated floating inductor.

Fig. 7 – Frequency response of fourth order Butterworth LPF.

Fig. 8 – HPF based on the proposed inductor.

### 5 Conclusions

This paper presents a compact configuration of modified CDTA (M-CDTA) and its application as the realization of floating inductance simulator, band pass filter and normalized fourth order butterworth low pass filter. The inductance simulated has several advantages such as: 1) only one passive component, i.e., a grounded capacitor is used; 2) no matching constraints (lossless); 3) electronically controllable

Table 1 – A table of comparison with few existing floating inductors available in literature.

| References | Number of active building blocks | Number of passive elements | Technology used      | Tunability | Type of capacitor used (F-floating G-grounded) | Matching conditions |

|------------|----------------------------------|----------------------------|----------------------|------------|------------------------------------------------|---------------------|

| [2]        | 2                                | 3                          | $0.35~\mu m / MOS$   | None       | F                                              | Yes                 |

| [3]        | 3                                | 1                          | MOS                  | None       | G                                              | No                  |

| [5]        | ≥2                               | ≥3                         | $0.35~\mu m / MOS$   | None       | G                                              | Yes                 |

| [6]        | 2                                | 3                          | $0.35 \ \mu m / MOS$ | Resistor   | G                                              | No                  |

| [7]        | 2                                | 3                          | $0.35 \ \mu m / MOS$ | None       | G                                              | Yes                 |

| [8]        | 2                                | 3                          | $0.25~\mu m$ /MOS    | Current    | G                                              | No                  |

| [9]        | 1                                | 3                          | $0.35 \ \mu m / MOS$ | None       | G                                              | No                  |

| [13]       | 2                                | 3                          | $0.25~\mu m/MOS$     | None       | G                                              | No                  |

| [14]       | <u>≥</u> _3                      | 4                          | BJT                  | None       | G                                              | No                  |

| [15]       | 1                                | 4                          | $0.18  \mu m / MOS$  | None       | F                                              | Yes                 |

| [16]       | 2                                | 1                          | BJT                  | Current    | G                                              | No                  |

| [17]       | 4                                | 4                          | MOS                  | Voltage    | G                                              | No                  |

| [18]       | 3                                | 1                          | $0.35 \ \mu m / MOS$ | Current    | G                                              | No                  |

| [19]       | 3                                | 1                          | BJT                  | None       | G                                              | No                  |

| [20]       | 2                                | 2                          | $0.25~\mu m$ /MOS    | Current    | G                                              | No                  |

| [21]       | 3                                | 1                          | BJT                  | Current    | G                                              | No                  |

| [22]       | 2                                | 3                          | $0.18  \mu m / MOS$  | None       | G                                              | No                  |

| [23]       | 1                                | 2                          | $0.5~\mu m / MOS$    | Current    | G                                              | No                  |

| [24]       | 2                                | 3                          | $0.13  \mu m / MOS$  | None       | G                                              | No                  |

| [25]       | 1                                | 2                          | $0.18~\mu m$ /MOS    | Current    | G                                              | No                  |

| Proposed   | 1                                | 1                          | $0.5~\mu m / MOS$    | Current    | G                                              | No                  |

using bias current; 4) low sensitivity. The SPICE simulations results are also included to justify the work proposed here.

### Acknowledgement

This research is supported by the "Young Faculty Research Fellowship and Research/Contingency Grant" awarded to Prof. Dinesh Prasad, Jamia Millia Islamia, under "Visvesvaraya Ph D Scheme for Electronics and IT" in 2015-16 from MEITY, Government of India.

### References

- Psychalinos C & Spanidou A, Int J Electron Commun, 60 (2006) 168.

- 2 Yuce E, Int J Electron, 94 (2007) 317.

- 3 Prasad D, Bhaskar D R & Singh A K, Radioengineering, 19 (2010) 194.

- 4 Sagbas M, Ayten U E, Sedef H & Koksal M, Int J Electron Commun, 63 (2009) 423.

- 5 Yuce E & Minaei S, *Microelectron J*, 40 (2009) 928.

- 6 Yuce E, Int J Electron, 97 (2010) 249.

- 7 Ibrahim M A, Minaei S, Yuce E, Herencsar N & Koton J, Radioengineering, 21 (2012) 3.

- 8 Ayten U E, Sagbas M, Herencsar N & Koton J, Radioengineering, 21 (2012) 11.

- 9 Yuce E, Int J Electron Commun, 61 (2007) 453.

- Toumazou C, Lidgey F J & Haigh D G, Analogue IC design: The current-mode approach, (Peter Peregrinus: London), 1990.

- 11 Bhaskar D R, Sharma V K, Monis M & Rizvi S M I, Microelectron J, 30 (1999) 837.

- Biolek D, CDTA building block for current-mode analog signal processing, In: Proceedings of the ECCTD'03, Krakow, Poland, 3 (2003) 397.

- 13 Yuce E & Minaei S, IEEE Trans Circuits Syst, 55 (2008) 266.

- 14 Yuce E, Analog Integr Circuits Signal Process, 49 (2006)

- 15 Said L A, Madian A H, Ismail M H & Soliman A M, Int J Electron Commun, 65 (2011) 753.

- 16 Sedef H, Sagbas M & Acar C, Int J Electron Commun, 95 (2008) 425.

- 17 R Senani, Bhaskar D R, Gupta S S & Singh V K, Int J Circuit Theory Appl, 37 (2009) 709.

- 18 Siripruchyanun M & Jaikla W, Int J Electron Commun, 62 (2008) 277.

- 19 Yuce E, Minaei S & Cicekoglu O, *Electr Eng*, 88 (2006) 519.

- 20 Herenscar N, Lahiri A, Koton J, Vrba K & Sotner R, Proceedings of the 22<sup>nd</sup> International Conference on Radio-elektronika, (2012) 1.

- 21 Li Y A, Int J Electron Commun, 66 (2012) 587.

- 22 Horng J W, Analog Integr Circuits Signal Process, 62 (2010) 407.

- 23 Tangsrirat W, Indian J Eng Mater Sci, 20 (2013) 79.

- 24 Manhas P S & Pal K, Arab J Sci Eng, 36 (2011) 1313.

- 25 Prasad D & Ahmad J, Circuits Systems, (2014) 13.

- 26 Prasad D, Bhaskar D R & Singh A K, Int J Electron Commun, 63 (2009) 497.