# Thermal stability analysis and performance exploration of asymmetrical dual-k underlap spacer (ADKUS) SOI FinFET for high performance circuit applications

Neeraj Jain & Balwinder Raj\*

Department of Electronics and Communication Engineering, Dr B R Ambedkar National Institute of Technology (NIT), Jalandhar 144 011, India

Received 31 October 2017; accepted 8 February 2019

This paper explores the performance of asymmetrical dual-k underlap spacer (ADKUS) SOI FinFET (device-D1) over the wide temperature range (200 K-450 K). An attempt has been made to find out the zero temperature coefficient (ZTC) biased point to enhance the digital, analog and RF performance at 20 nm channel length. The proposed device will be suitable for VLSI circuit's design, internet of things (IoT) interfacing components and algorithm development for security applications of information technology. The potential parameters of device-D1 like intrinsic gain ( $A_V$ ), output conductance ( $g_d$ ), transconductance ( $g_m$ ), early voltage ( $V_{EA}$ ), off current ( $I_{off}$ ), on current ( $I_{on}$ ),  $I_{on}/I_{off}$  ratio, gate to source capacitance ( $C_g$ ), gate to drain capacitance ( $C_g$ ), cut-off frequency ( $f_T$ ), energy (CV²), intrinsic delay (CV/I), energy-delay product (EDP), power dissipation (PD), sub-threshold slope (SS), Q-Factor ( $g_{m,max}$ /SS), threshold voltage ( $V_{th}$ ) and maximum transconductance ( $g_{m,max}$ ) are subjected to analyze for evaluating the performance of ADKUS SOI FinFET for wide temperature environment. The validation of a temperature based performance of ADKUS SOI FinFET gives an opportunity to design the numerous analog and digital components of internet security infrastructure at wide temperature environment. These ADKUS SOI FinFET based components give new technology to the IoT which has the ability to connect the real world with the digital world and enables the people and machines to know the status of thousands of components simultaneously.

**Keywords:** ADKUS SOI FinFET, CMOS, Transconductance, Analog/RF performance, Intrinsic gain, Temperature, Capacitance

#### 1 Introduction

Today requirement of low power and highperformance devices in the consumer products has become the driving force to develop the new technology in the semiconductor industries. The invention of FinFET greatly enables the development of complex integrated circuits for a variety of applications due to its 3-D(dimensional) quasi-planar geometry<sup>1</sup>. The developments in semiconductor devices are bringing improvements in VLSI circuits design, internet infrastructure and algorithms for security and privacy applications of information technology<sup>2</sup>. FinFET is one of the most desirable multi-gate structure in CMOS technology due to its high immunity to short channel effects (SCE's), excellent scalability and very close to MOSFET in respect to layout design<sup>3</sup>. The analog components based on FinFET technology used in sensors (temperature, motion, pressure, shock, proximity, sound, gas, infrared, etc.), amplifiers, signal processors, microcontroller and integrated chips give

better technology to the internet of things (IoT) applications<sup>4–7</sup>. Therefore, world top semiconductor leading industries like TSMC and Cadence designed the FinFETs at 7 nm technology node for security and high-performance computing platforms and others companies are further trying to improve the performance of FinFET by optimizing the underlap spacer region at lower technology nodes<sup>8,9</sup>. However, there is always a tradeoff among SCEs and analog/RF performance of FinFET. Further, improvement in FinFET structure has been done through SOI layer, and source/drain engineering spacer techniques 10,11. As per demand for variety of applications in the semiconductor industries, a lot of advanced device structures proposed in literature like pi-gate<sup>12,13</sup>, ohm-gate<sup>14</sup>, tri-gate, planar double gate SOI MOSFETs, Bulk FinFETs, SOI FinFETs and all around gate 15-19. According to literature, significant work already proposed with dual-k and high-k spacers to improve the SCEs and analog/RF performances of underlap SOI FinFETs <sup>20,21</sup>. Similarly, Pal et al. <sup>9,22</sup> demonstrate the asymmetric dual-k spacers and symmetrical SOI FinFET structures for a highperformance application. Goel et al. 23,24

<sup>\*</sup>Corresponding author (E-mail: balwinderraj@gmail.com)

elaborated the asymmetrical dual-k spacer SOI FinFET structure for low power and digital SRAM applications. Beside these, some applications like automobiles, military and nuclear sectors require high temperature operated integrated circuits (ICs) and other like medical diagnostic systems and space applications require low temperature based operated equipment. Some industries demand both high and low-temperature sustainable ICs for their application. FinFETs are the devices which fulfill the requirement of these ICs and chip industries are now trying to implement the FinFET circuits in all electronic gadgets like computer chips, mobile phones and sensor-based high performance security and privacy systems.

This work demonstrates the effect of dual-k underlap spacer at the drain side on the analog/RF performance of ADKUS SOI FinFET investigation is done for the ZTC point over the wide temperature range. As compared to conventional bulk FinFET this architecture enhances the analog and RF performance of complex integrated circuits without increasing the effective chip area. The ADKUS SOI FinFET device with combination of dual- k spacers (inner underlap side of gate high-k (HfO<sub>2</sub>) and outer side the low-k (Si<sub>3</sub>N<sub>4</sub>)) at the drain side is explored for wide temperature range. The performance of ADKUS SOI FinFET is analyzed in terms of analog/RF performance parameters like  $I_{\rm on}$ ,  $I_{\rm off}$ ,  $I_{\rm on}/I_{\rm off}$ , output conductance  $(g_d)$ , transconductance  $(g_m)$ , transconductance generation factor (TGF), subthreshold slope (SS), intrinsic gain  $(A_V)$ , early voltage  $(V_{\rm EA})$ , gate capacitance  $(C_{\rm gg})$ , gate to source capacitance  $(C_{gs})$ , gate to drain capacitance  $(C_{gd})$  and cut-off frequency  $(f_T)$  etc.

The sensitivity of ADKUS SOI FinFET in the temperature range 200 K-400 K towards analog/RF

design is very crucial and the investigation is done for ZTC bias point using 3D simulations process. ZTC bias point is an important parameter which describes the stability of semiconductor device and shows the current-voltage negligible variation in characteristic with temperature. The previous literature works by Mohapatra et al.25 and Sahu et al.26 have been done with ZTC bias point for MOSFETs stability analysis. In this paper, demonstration of ADKUS SOI FinFET for stability analysis has been done by ZTC bias point over the wide temperature range (200 K- 450 K). As compared to MOSFET, SOI FinFET gives better temperature performance at sub-20 nm technology node.

# 2 Structures and Simulation Setup

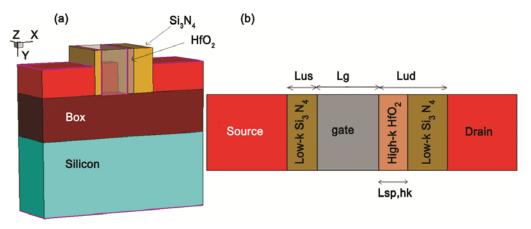

Schematic diagram of asymmetrical dual-k underlap spacer (ADKUS) SOI FinFET structure is shown in Fig. 1(a). For this FinFET structure, 20 nm channel length is considered for 3D- simulations. Source/drain part of ADKUS SOI FinFET structure is heavily doped as n-type  $1 \times 10^{20}$  cm<sup>-3</sup> and the channel region of the FinFET structure is lightly doped as ptype 1×10<sup>15</sup> cm<sup>-3</sup>. Source/drain is heavily doped to overcome the effect of mobility degradation which is the effect of coulomb charge scattering. Here the total effective width of FinFET device  $W = (2H_{Fin} + W_{Fin})$ is considered because the total current of the FinFET structure at sub-20 nm technology node is the effective sum of all current components flowing along the sidewalls and the top surfaces of Fin<sup>27</sup>. Metal gate technology is used in ADKUS SOI FinFET structure because it eliminates the poly gate depletion effect in all semiconductor devices. The length of source /drain is fixed to 40 nm with vertically placed source and

Fig. 1 – (a) Asymmetrical dual-k underlap spacer SOI FinFET (device-D1) and (b) cross-section view of device D.

drain contacts, respectively. Device dimensional parameters of ADKUS SOI FinFET device used for 3D simulation in this paper are given in Table 1.

Figure 1(b) shows the cross-section view of ADKUS SOI FinFET structure in which dual-k spacer is used for underlap region at the drain side. Underlap region (Lud) which is a combination of two high-k (gate side, Lsp, hk) and low-k (drain side, Lsp, lk) materials. At the source side low-k (Si<sub>3</sub>N<sub>4</sub>) spacer material is used. The high-k spacer is used to increase the  $I_{\rm on}$  current of FinFET by optimizing the gate induced barrier lowering (GIBL) while the low-k spacer is used to optimize the effect of parasitic extrinsic capacitances. In conventional FinFETs, the high-k spacer at the drain side improves the driving current with a significant reduction of off-state leakage current. However, these devices suffer by increased total effective gate fringing capacitances which results in poor device cut-off frequency  $(f_T)$  and circuit level delay<sup>28</sup>. So dual-k spacer is used to get optimum analog and RF performance at lower technology node. A substrate with a lightly doped concentration of  $1 \times 10^{15}$  cm<sup>-3</sup> is used to minimize the effect of random dopants fluctuations in ADKUS SOI FinFETs for performances analysis<sup>29</sup>.

The underlap region in SOI FinFET increases the distributed channel resistance or degradation in  $I_{\rm on}$  current and faces the problem of controlling the doping profile. However, these problems are well tackled in literature<sup>30–32</sup>. The asymmetric underlap region at drain side for MOSFETs and degradation in  $I_{\rm on}$  can be improved further by introducing inner high-k spacer in underlap region without any significant degradation of output fringing capacitance<sup>33</sup>.

The ADKUS SOI FinFET structure follows the standard FinFET process flow<sup>34</sup>. In ADKUS SOI FinFET process flow, prior fabrication of source-drain lateral extension region, spacer regions are fabricated. Initially, the dual-k spacer region is engineered in the

FinFET device and fabrication of dual-k region follows the two-step process. In first step formation of high-k spacer using selective epitaxial growth technique at the drain side followed by the second step in which low-k offset spacer is formed both at the source and drain side side spacer is formed both at the drain side kept longer to ensure asymmetric underlap region during source/drain extension region fabrication by tilt ion implantation second step second seco

The 3-D simulations of ADKUS SOI FinFET structure are carried out using Sentaurus TCAD simulator tool<sup>41</sup>. Analog/RF performance of device D1 is explored at 200 K-450 K temperature range for total length<sup>24</sup> under drain side of 20 nm. The metal gate work function is set to 4.3 eV. The equivalent oxide thickness $^{42-44}$  ( $t_{0x}$ ) is taken a value of 0.9 nm at the supply voltage  $V_{\rm DD}$  of 0.7 V and other parameters considered according to International Technology Roadmap for Semiconductors<sup>45</sup> (ITRS-2013). The simulation validation of simulator is investigated by reported results in the previous literature data<sup>44</sup>. The models considered in this paper are velocity saturation model, concentration-dependent and field dependent mobility that consider the doping models<sup>46</sup>. The inversion mobility Lombardi CVT<sup>47</sup>, models of auger recombination with Shockley –Read-Hall (SRH)<sup>47–49</sup>, default carrier transport model and quantum confinement are also considered for simulation process. Junctions with smooth meshing and all biasing are done at a wide range of temperatures to evaluate the performance of ADKUS SOI FinFET structure.

### 3 Results and Discussion

In this section, the performance of ADKUS SOI FinFET (Device-D1) in terms of energy (CV<sup>2</sup>), intrinsic delay (CV/I), energy-delay product (EDP), power dissipation (PD), sub-threshold slope (SS), Q-Factor ( $g_{m,max}$ /SS), threshold voltage ( $V_{th}$ ), maximum trans-conductance ( $g_{max}$ ), on current ( $I_{on}$ ), off current

| Table 1 – Dimensional values used for simulation in this paper.          |                                 |                             |  |  |  |

|--------------------------------------------------------------------------|---------------------------------|-----------------------------|--|--|--|

| Parameters                                                               | Descriptions                    | Device-D1                   |  |  |  |

| $W_{ m Fin}$                                                             | Fin width                       | 10 nm                       |  |  |  |

| $L_{ m g}$                                                               | Gate channel length             | 20 nm                       |  |  |  |

| $H_{\mathrm{Fin}}$                                                       | Fin height                      | 26 nm                       |  |  |  |

| $t_{ m ox}$                                                              | Oxide thickness                 | 0.9 nm                      |  |  |  |

| BOX                                                                      | Thickness of buried oxide       | 40 nm                       |  |  |  |

| L                                                                        | Total length of device          | 120 nm                      |  |  |  |

| Lus =Lsp,hk (HfO <sub>2</sub> )+Lsp,lk (Si <sub>3</sub> N <sub>4</sub> ) | Spacer length under source side | Lsp, hk=0 nm, Lsp, lk=5 nm  |  |  |  |

| Lud =Lsp,hk (HfO <sub>2</sub> )+Lsp,lk (Si <sub>3</sub> N <sub>4</sub> ) | Spacer length under drain side  | Lsp, hk=5 nm, Lsp, lk=15 nm |  |  |  |

| $W_{ m s/d}$                                                             | Source/drain width              | 40 nm                       |  |  |  |

$(I_{\rm off})$ ,  $I_{\rm on}/I_{\rm off}$  ratio and the analog/RF performance intrinsic parameters like gain  $(A_{\rm V})$ , conductance  $(g_d)$ , transconductance  $(g_m)$ , early voltage  $(V_{\rm EA})$ , gate to source capacitance  $(C_{\rm gs})$ , gate to drain capacitance ( $C_{\rm gd}$ ), total gate capacitance ( $C_{\rm gg}$ ) and cut off frequency  $(f_T)$  are evaluated for various temperature range (200 K to 450 K) for the low and high value of drain to source voltages  $V_{DS}$ =0.05 V and  $V_{\rm DS}$ =0.7 V, respectively. The temperature variation in the semiconductor device severely affects its electrical characteristics parameters like mobility, sub-threshold slope, threshold voltage, leakage current, power dissipation and intrinsic delay becomes the major concern in the scaled technology design.

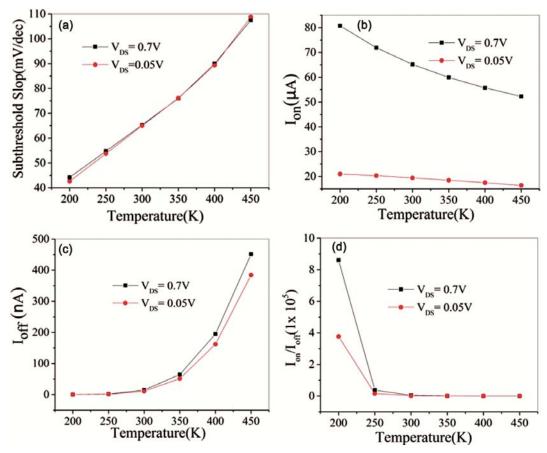

Figure 2 shows some device scalability performance characteristics of ADKUS SOI FinFET like SS,  $I_{\rm on}$ ,  $I_{\rm off}$ ,  $I_{\rm on}$ /  $I_{\rm off}$  ratio with temperature variation at  $V_{\rm DS}$ =0.05 V and  $V_{\rm DS}$ =0.7 V. It is noticed from the Fig. 2(a) that on increasing the temperature subthreshold performance of device degraded due to the reduction of  $I_{\rm on}$  current both at a low and high value of  $V_{\rm DS}$ =0.05 V and  $V_{\rm DS}$ =0.7 V, respectively. SS is an

important parameter which describes the  $I_{\rm off}$  leakage current and related with temperature<sup>50</sup> according to as follows:

$$SS(mV / decade) \approx 60mV \frac{T}{300K}$$

...(1)

According to Eq. (1), at a low temperature range (below 250 K), there is much reduction of SS value that directly reflects the off state leakage current of the semiconductor device and improvement in  $I_{\rm off}$  at lower temperature range is shown in Fig. 2(c). So, at low temperature (below 250 K), there is a noticeable improvement in  $I_{\rm on}/I_{\rm off}$  ratio due to a significant reduction of  $I_{\rm off}$  current because of the low value of sub-threshold slope (SS) as shown in Fig. 2(d). The high value of  $I_{\rm on}/I_{\rm off}$  and low value of  $I_{\rm off}$  is desirable for low power analog circuit applications.

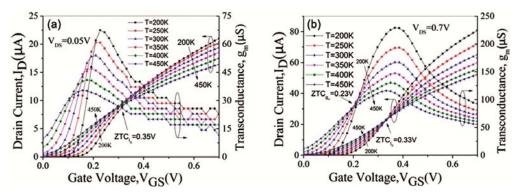

The drain current  $(I_{\rm D})$  and transconductance  $(g_{\rm m})$  against gate-source voltage  $(V_{\rm GS})$  characteristics for various values of temperature range (200 K-450 K) at  $V_{\rm DS}$ =0.05 V and  $V_{\rm DS}$ =0.7 V for ADKUS SOI FinFET are shown in Fig. 3(a) and (b), respectively. The drain

Fig. 2 – (a) Sub-threshold slope (SS), (b) on current ( $I_{\rm on}$ ), (c) off current ( $I_{\rm off}$ ) and (d)  $I_{\rm on}/I_{\rm off}$  ratio versus temperature characteristics for ADKUS SOI FinFET at  $V_{\rm DS}$ = 0.05 V and  $V_{\rm DS}$ = 0.7 V.

Fig. 3 –  $I_D$  and  $g_m$  versus  $V_{GS}$  characteristics of ADKUS SOI FinFET with temperature variation at (a)  $V_{DS}$ =0.05 V and (b)  $V_{DS}$ =0.7 V.

current as a function of mobility ( $\mu$ ) and threshold voltage<sup>51</sup> ( $V_{th}$ ) is as follows:

$$I_D(T) \propto \mu(T)[V_{GS} - V_{th}(T)] \qquad \dots (2)$$

The mobility term and threshold voltage both are temperature dependent parameters. The carrier mobility follows the relationship as follows:

$$\mu(T) = \mu(T_0)(T/T_0)^{-n}$$

where n exponent<sup>50</sup> varies from 1.6 to 2.4.

The threshold voltage of SOI devices follows the inverse temperature characteristics and decreases with the increase of temperature<sup>52</sup>. On increasing the temperature, mobility of charge carrier also decreases for ADKUS SOI FinFET due to lattice scattering effects. So,  $\mu(T)$  and  $[V_{GS} - V_{th}(T)]$  terms of drain current shown in Eq. (2) will show the inverse nature with temperature variation. As increasing the temperature,  $\mu(T)$  value decreases which tries to force drain current decrease while the value of  $[V_{GS} - V_{th}(T)]$ term increases which tries to force drain current increases. So on increasing the gate bias point, these two effects compensated at a fixed value of gate to source voltage  $(V_{GS})$  and effect of temperature variation at this point can be neglected for evaluating the performance of ADKUS SOI device. This gate bias point is known as zero temperature coefficients (ZTC) point.

As we observe from the  $I_{\rm D}$ - $V_{\rm GS}$  characteristics shown in Fig. 3 that for low and high  $V_{\rm DS}$  value below the  $ZTC_{I_D}$  point, drain current ( $I_{\rm D}$ ) increases with increasing the temperature while above the  $ZTC_{I_D}$  point nature of drain current becomes the opposite. As  $V_{\rm GS} < V_{\rm th}$ , current mainly flows by a diffusion process. So, below the  $ZTC_{I_D}$  point,  $[V_{\rm GS} - V_{\rm th}(T)]$  becomes the dominating factor as compared to  $\mu(T)$  due to more

degradation of the threshold at a high value of temperature. So, drain current increases with the increase of temperature value. As  $V_{\rm GS} > V_{\rm th}$ , the dominating flow of current is by drift process. So, above the  $ZTC_{I_D}$  point,  $\mu(T)$  decreases with the increase of temperature due to more lattice scattering effect and becomes the dominating factor for evaluating the drain current. So, drain current decreases with the increase of temperature value.

In Fig. 3(b), at  $V_{DS}$ = 0.7 V, we extract the two ZTC points for drain bias and trans-conductance bias  $ZTC_{I_n}$  and  $ZTC_{g_m}$ , respectively. Both these ZTC points are important figures of merit for analog circuit design at various temperature values. The  $ZTC_{I_D}$  bias point gives the information about constant DC current while  $ZTC_{\sigma}$  bias point is used to achieve stable circuit parameters for analog design. Both bias points are affected by the process variation. So, ZTC points are chosen according to the applications. It is noticed from the Fig. 3(b) that the extracted value of  $ZTC_{g_{m}} = 0.23V$  and  $ZTC_{I_{D}} = 0.33V$  at  $V_{DS} = 0.7$  V. So, below 0.23 V the trans-conductance (g<sub>m</sub>) increases due to degradation of V<sub>th</sub> on increasing the temperature while above 0.23 V the g<sub>m</sub> decreases due to the reduction of channel mobility by lattice scattering effects on increasing the temperature.

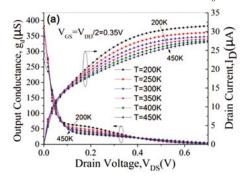

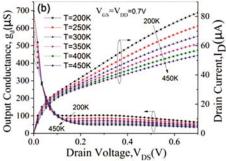

The output performance characteristics of ADKUS SOI FinFET, drain current  $(I_D)$  and output conductance  $(g_d)$  versus drain-source voltage  $(V_{DS})$  at  $V_{GS}$ = 0.35 V and  $V_{GS}$ = 0.7 V are shown in Fig. 4 (a and b), respectively. From the Fig. 4(a and b), it is noticed that above the  $ZTC_{I_D}$  point, drain current decreases on increasing the temperature due to discussed  $\mu(T)$  effect with temperature and opposite nature of current generated below the  $ZTC_{I_D}$ . The low

value of  $g_d$  is required to improve the intrinsic gain  $(g_m/g_d)$  of ADKUS SOI FinFET device. Further,  $g_d$  is less sensitive to temperature at  $V_{GS}$ = 0.35 V compare to  $V_{GS}$ = 0.7 V near the ZTC point of  $g_d$  and it can be analyzed from Fig. 4.

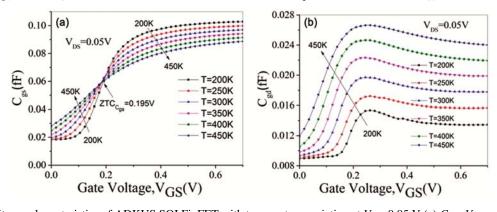

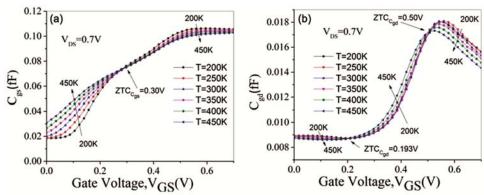

Figure 5 (a and b) and Fig. 6 (a and b) shows the gate to source capacitance ( $C_{\rm gs}$ ) and gate to drain capacitance ( $C_{\rm gd}$ ) versus  $V_{\rm GS}$  characteristics for ADKUS SOI FinFET at  $V_{\rm DS}$ = 0.05 V and  $V_{\rm DS}$ =0.7 V, respectively. From Fig. 5 (a) and (b), it is noticed that at  $V_{\rm DS}$ =0.05V, ZTC for  $C_{\rm gs}$  ( $ZTC_{C_{\rm gs}}$ ) has a value of 0.195 V without having the ZTC for  $C_{\rm gd}$  ( $ZTC_{C_{\rm gd}}$ ).

The  $C_{\rm gs}$  increases with increasing the temperature below  $ZTC_{C_{\rm gs}}$  point whereas opposite nature of  $C_{\rm gs}$  occurs above the  $ZTC_{C_{\rm gs}}$  point. In case of  $C_{\rm gd}$ , it increases with gate bias in weak inversion region and has more value at high temperature after that it decreases in the strong inversion region with gate bias. It is noticed from the Fig. 6(a) that  $ZTC_{C_{\rm gs}}$  has the value of 0.3 V at  $V_{\rm DS}$ =0.7 V and follow the same nature as at  $V_{\rm DS}$ =0.05 V. In case of  $C_{\rm gd}$ , two ZTC points generated at  $V_{\rm DS}$ = 0.7 V due to dual-k spacer region at the drain side for ADKUS SOI FinFET. The variation of these two ZTC points is due to fringing

Fig. 4 –  $I_D$  and  $g_d$  versus  $V_{DS}$  characteristics of ADKUS SOI FinFET with temperature variation at (a)  $V_{GS}$ =0.35 V and (b)  $V_{GS}$ =0.7 V.

Fig. 5 – Capacitance characteristics of ADKUS SOI FinFET with temperature variation at  $V_{DS}$ =0.05 V (a)  $C_{gs}$  -  $V_{GS}$  and (b)  $C_{gd}$  -  $V_{GS}$ .

Fig. 6 – Capacitance characteristics of ADKUS SOI FinFET with temperature variation at  $V_{DS}$ =0.7 V (a)  $C_{gs}$  -  $V_{GS}$  and (b)  $C_{gd}$  -  $V_{GS}$ .

field modulation of high-k and low-k spacers at the drain side. So the optimum value of  $C_{\rm gd}$  can be generated for wide temperature range according to required DC and analog/RF circuit applications.

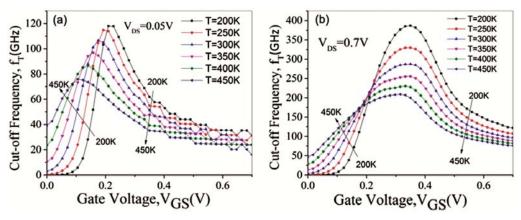

The cut-off frequency

$$f_T = \frac{g_m}{2\pi(C_{gs} + C_{gd})}$$

is an

important parameter for evaluating the RF performance of ADKUS FinFET. The cut-off frequency  $(f_{\rm T})$  versus  $V_{\rm GS}$  characteristics with temperature variation at  $V_{\rm DS}$ =0.05 V and  $V_{\rm DS}$ =0.7 V are shown in Fig. 7 (a) and (b), respectively. It is noticed from the Fig.7 that in weak inversion region improvement in cut off frequency  $(f_{\rm T})$  occurs on increasing the temperature while opposite nature of cut off frequency  $(f_{\rm T})$  occurs in strong inversion region. At  $V_{\rm DS}$ =0.7 V, above the ZTC point of  $f_{\rm T}$ , improvement in  $f_{\rm T}$  occurs due to the steep improvement of charge carrier mobility for a low value of temperature range.

Table 2 shows the some extracted performance parameters for ADKUS SOI FinFET at  $V_{\rm DS}$ =0.7 V for a wide temperatures range. From the extracted results of Table 2, it is noticed that there is improvement in intrinsic delay (CV/I), energy-delay product (EDP), off state power dissipation (PD =  $I_{\rm off}$ \* $V_{\rm DD}$ ), SS value,  $g_{\rm m,max}(S)$ ,  $I_{\rm on}/I_{\rm off}$  and Q-Factor ( $g_{\rm m,max}/SS$ ) for low

value of temperature. Q-factor and EDP are important figures of merit for circuit applications and these parameters improved due to the low value of SS and intrinsic delay at low temperature.

Analog/RF performance parameters like  $g_{\rm m}$ ,  $g_{\rm d}$ ,  $A_{\rm v}(g_{\rm m}/g_{\rm d})$ ,  $V_{\rm EA}$ ,  $C_{\rm gg}$ ,  $C_{\rm gs}$ ,  $C_{\rm gd}$  and  $f_{\rm T}$  for ADKUS SOI FinFET for wide temperature range (200 K-450 K) are also evaluated at  $V_{\rm DS}$ =0.7 V and shown in Table 3. It is noticed from Table 3 that there is a significant improvement in intrinsic gain  $(A_{\rm v})$  and much improvement in cut-off frequency  $(f_{\rm T})$  at a lower value of temperature. This improvement occurs due to the increased value of  $g_{\rm m}$  at lower temperature range.

# **4 Implications for Practice**

Today world economy directly or indirectly depends on the semiconductor industries. In early days, consumer products like mobile phone, car, watch and even refrigerator have more power as compare to the early computers. Now, we are moving fast towards and more connected world, a world of internet of things where our consumer appliances are able to communicate each other with the more efficient with less cost. This is being possible only due to improvement in the basic unit (transistor) of More numbers of chip industries. integrated the chip increase into the

Fig. 7 – Cut-off frequency ( $f_T$ ) versus  $V_{GS}$  characteristics with temperature variation at (a)  $V_{DS}$ =0.05 V and (b)  $V_{DS}$ =0.7 V.

| Table 2 – Extracted performance metrics of ADKUS SOI FinFET for various temperatures at $V_{DS}$ =0.7 V. |                                          |                |                                |                                       |                   |                                          |                |                                                                       |                                   |

|----------------------------------------------------------------------------------------------------------|------------------------------------------|----------------|--------------------------------|---------------------------------------|-------------------|------------------------------------------|----------------|-----------------------------------------------------------------------|-----------------------------------|

| Temperature(K)                                                                                           | Energy (CV $^2$ )<br>(Joule)×10 $^{-17}$ |                | EDP<br>(Js) ×10 <sup>-28</sup> | PD $(I_{\text{off}} * V_{\text{DD}})$ | SS<br>(mV/decade) | $I_{\text{on}}/I_{\text{off}}$           | $V_{th}$       | $\begin{array}{c} g_{m,ma\times} \\ (S) \ \times 10^{-4} \end{array}$ | Q-factor (g <sub>m,max</sub> /SS) |

| 200                                                                                                      | 4.546                                    | (ps)<br>2.412  | 1.097                          | (nW)<br>0.066                         | 44.186            | $8.62 \times 10^{5}$                     | 0.233          | 2.29                                                                  | ×10 <sup>-3</sup> 5.18            |

| 250                                                                                                      | 4.487                                    | 2.412          | 1.108                          | 1.335                                 | 54.758            | $3.77 \times 10^4$                       | 0.215          | 1.93                                                                  | 3.53                              |

| 300<br>350                                                                                               | 4.458<br>4.452                           | 2.511<br>2.537 | 1.119<br>1.129                 | 10.33<br>45.29                        | 65.303<br>76.022  | $4.42 \times 10^3$<br>$9.26 \times 10^2$ | 0.199<br>0.179 | 1.67<br>1.47                                                          | 2.56<br>1.94                      |

| 400                                                                                                      | 4.468                                    | 2.556          | 1.142                          | 136.6                                 | 89.967            | $2.86 \times 10^{2}$                     | 0.159          | 1.30                                                                  | 1.45                              |

| 450                                                                                                      | 4.502                                    | 2.576          | 1.160                          | 316.3                                 | 107.47            | $1.16 \times 10^{2}$                     | 0.135          | 1.16                                                                  | 1.08                              |

| Table 3 – Extracted analog/RF performance parameters for ADKUS SOI FinFET for various temperature values at $V_{DS}$ =0.7 V. |                    |                    |                    |                    |                    |                    |  |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|--|

| Analog/RF<br>extracted<br>performance<br>metrics                                                                             | Temperature= 200 K | Temperature= 250 K | Temperature= 300 K | Temperature= 350 K | Temperature= 400 K | Temperature= 450 K |  |  |

| $g_m(\mu S)$                                                                                                                 | 225                | 190                | 164                | 146                | 130                | 115                |  |  |

| $g_d(\mu S)$                                                                                                                 | 3.53               | 3.11               | 2.61               | 2.63               | 3.64               | 5.39               |  |  |

| $A_V(dB)$                                                                                                                    | 36.10              | 35.69              | 35.97              | 34.88              | 31.09              | 26.59              |  |  |

| $V_{EA}(V)$                                                                                                                  | 8.92               | 9.57               | 11.00              | 10.67              | 7.59               | 5.05               |  |  |

| $C_{gg}(aF)$                                                                                                                 | 92.8               | 91.6               | 91                 | 90.9               | 91.2               | 91.9               |  |  |

| $C_{gs}(aF)$                                                                                                                 | 82.8               | 81.6               | 81                 | 80.8               | 80.9               | 81.2               |  |  |

| $C_{gd}(aF)$                                                                                                                 | 9.94               | 9.94               | 9.96               | 10.1               | 10.3               | 10.7               |  |  |

| $C_{gs}/C_{gd}$                                                                                                              | 8.33               | 8.22               | 8.13               | 8.02               | 7.83               | 7.58               |  |  |

| f <sub>T</sub> (GHz)                                                                                                         | 387                | 330                | 287                | 255                | 228                | 200                |  |  |

functionality of consumer products like mobile phones, tablets, computer peripherals, industrial equipment, military and security automation applications. More transistors on a single chip can be done with smaller size transistor with less power consumption and this can be done by FinFET transistor technology. Chips can perform more and more tasks while becoming smaller at the same time, thus enabling their use in countless devices that improve our lives in multi-ways. So, with this innovated technology, more featured electronics gadgets and industrial automated equipment can be implemented at lower cost in the industries which indirectly reflect the economy of a country.

#### **5 Conclusions**

In this paper, ADKUS SOI FinFET is explored in terms of performance parameters like intrinsic delay (CV/I), energy-delay product (EDP), off state power dissipation (PD =  $I_{\text{off}} * V_{\text{DD}}$ ), SS value,  $g_{m,max}(S)$ ,  $I_{on}/I_{off}$  , Q-Factor  $(g_{m,max}/SS)$  and analog/RF parameters like  $g_{\rm m}$ ,  $g_{\rm d}$ ,  $A_{\rm v}(g_{\rm m}/g_{\rm d})$ ,  $V_{\rm EA}$ ,  $C_{\rm gg}$ ,  $C_{\rm gs}$ ,  $C_{\rm gd}$  and  $f_{\rm T}$  for wide temperature range (200 K-450 K). The analysis is done on the basis of zero temperature coefficient (ZTC) for drain current and transconductance bias point for low and hightemperature range. Above and below the ZTC point ADKUS SOI FinFET has opposite nature. So, it is concluded that with the help of ZTC point, ADKUS SOI FinFET can be biased for DC, analog and RF applications for wide temperature range and effect of temperature variation on the device performance can be minimized at ZTC bias point. So, effective use of FinFET transistor for particular application improves the performance of semiconductor industry which reflects the economy and business of the country.

#### References

- Hisamoto D, Lee W C, Kedzierski J, Takeuchi H, Asano K, Kuo C, Anderson E, King T J, Jeffrey B F & Hu C, IEEE Trans Electron Devices, 47 (2000) 2320.

- 2 Gupta B, Agrawal D P & Yamaguchi S, Handbook of research on modern cryptographic solutions for computer and cyber security, (IGI Global), 2016.

- 3 Nowak E J, Aller I, Ludwig T, Kim K, Joshi R V, Chuang C T, Bernstein K & Puri R, *IEEE Circuits Devices Mag*, 20 (2004) 20.

- 4 Malek A B, Ahmadon M A B, Yamaguchi S & Gupta B B, Consumer Electronics, 5th Global Conference on IEEE, (2016) 1.

- 5 Memos V A, Psannis K E, Ishibashi Y, Kim B G & Gupta B B, Futur Gener Comput Syst, (2017).

- 6 Tewari A & Gupta B B, J Supercomput, 73 (2017) 1085.

- 7 Chang V, Kuo Y H & Ramachandran M, Futur Gener Comput Syst, 57 (2016) 24.

- 8 Pal P K, Kaushik B K & Dasgupta S, *IEEE Trans Electron Devices*, 60 (2013) 3371.

- 9 Pal P K, Kaushik B K & Dasgupta S, IEEE Trans Electron Devices, 61 (2014) 3579.

- 10 Kranti A & Armstrong G A, Microelectron Eng, 84 (2007) 2775.

- 11 Virani H G, Adari R B R & Kottantharayil A, *IEEE Trans Electron Devices*, 57 (2010) 2410.

- 12 Jain A, Sharma S K & Raj B, Eng Sci Technol Int J, 19 (2016) 1864.

- 13 Park J T, Colinge J P & Diaz C H, *IEEE Electron Device Lett*, 22 (2001) 405.

- 14 Colinge J P & Chandrakasan A, FinFETs and other multigate transistors, (2008).

- 15 Singh N, Lim F Y, Fang W W, Rustagi S C, Bera L K, Agarwal A, Tung C H, Hoe K M, Omampuliyur S R, Tripathi D, Adeyeye A O, Lo G Q, Balasubramanian N & Kwong D L, In Technical Digest International Electron Devices Meeting, IEDM, (2006).

- 16 Sharma V K, Pattanaik M & Raj B, Int J Electron, 102 (2015) 200.

- 17 Raj B, Saxena A K & Dasgupta S, Microelectron Int, 26 (2009) 53.

- 18 Raj B, Saxena A K & Dasgupta S, *J Nanoelectron Optoelectron*, 3 (2008) 163.

- 19 Raj B, In Toward Quantum FinFET, Springer, (2013) 81.

- 20 Patil G C & Qureshi S, Semicond Sci Technol, 27 (2012) 045004.

- 21 Nandi A, Saxena A K & Dasgupta S, Microelectronics J, 43 (2012) 883.

- 22 Pal P K, Kaushik B K & Dasgupta S, *IEEE Trans Electron Devices*, 62 (2015) 1105.

- 23 Jain N & Raj B, Rev Adv Sci Eng, 5 (2016) 123.

- 24 Goel A, Gupta S K & Roy K, *IEEE Trans Electron Devices*, 58 (2011) 296.

- 25 Mohapatra S K, Pradhan K P & Sahu P K, Superlattices Microstruct, 78 (2015) 134.

- 26 Sahu P K, Mohapatra S K & Pradhan K P, Mater Sci Semicond Process, 31 (2015) 175.

- 27 Magnone P, Mercha A, Subramanian V, Parvais P, Collaert N, Dehan M, Decoutere S, Groeseneken G, Benson J & Merelle T, *IEEE Electron Device Lett*, 30 (2009) 1374.

- 28 Pradhan K P, Andrade M G C & Sahu P K, Superlattices Microstruct, 100 (2016) 335.

- 29 Nowak E J, IBM J Res Dev, 46 (2002) 169.

- 30 Trivedi V, Fossum J G & Chowdhury M M, *IEEE Trans Electron Devices*, 52 (2005) 56.

- 31 Koley K, Dutta A, Syamal B, Saha S K & Sarkar C K, *IEEE Trans Electron Devices*, 60 (2013) 63.

- 32 Sachid A B, Manoj C R, Sharma D K & Rao V R, *IEEE Electron Device Lett*, 29 (2008) 128.

- 33 Goel A, Gupta S, Bansal A, Chiang M H & Roy K, In 2009 Device Research Conference IEEE, (2009) 57.

- 34 Kedzierski J, Ieong M, Nowak E, Kanarsky T S, Zhang Y, Roy R, Boyd D, Fried D & Wong H S, *IEEE Trans Electron Devices*, 50 (2003) 952.

- 35 Lin J, Google Patents, 2 September, 1997.

- 36 Anderson B A, Bryant A, Clark Jr W F & Nowak E J, Google Patents, 7 March 2006.

- 37 Shields J A, Pham T D, Ramsbey M T, Sun Y, Hui A T & Chan M C, *Google Patents*, 14 March, 2006.

- 38 Lee B H & Mocuta A C, Google Patents, 8 June 2004.

- 39 Ghani T, Mistry K, Packan P, Armstrong M, Thompson S, Tyagi S & Bohr M, In VLSI Technology 2001, Digest of Technical Papers, Symposium on IEEE (2001) 17.

- 40 Ohuchi K, Adachi K, Hokazono A & Toyoshima Y, In Ion Implantation Technology, 2002 Proceedings of the 14th International Conference on IEEE, (2002) 7.

- 41 http://www.synopsys.com, In Synopsys Sentaurus Device, (2009) 191.

- 42 Pradhan K P, Mohapatra S K, Sahu P K & Behera D K, *Microelectronics J*, 45 (2014) 144.

- 43 Ho B, Sun X, Shin C & Liu T J K, *IEEE Trans Electron Devices*, 60 (2013) 28.

- 44 De Andrade M G C, Martino J A, Aoulaiche M, Collaert N, Simoen E & Claeys C, Solid-State Electron, 71 (2012) 63.

- 45 Internation Technology Roadmap for Semiconductors (ITRS), 80 (2013).

- 46 Canali C, Majni G, Minder R & Ottaviani G, *IEEE Trans Electron Devices*, 22 (1975) 1045.

- 47 Lombardi C, Manzini S, Saporito A & Vanzi M, *IEEE Trans Comput Des Integr Circuits Syst*, 7 (1988) 1164.

- 48 Shockley W & Read W T, Phys Rev, 87 (1952) 835.

- 49 Hall R N, Phys Rev, 87 (1952) 387.

- 50 Sze S M & Ng K K, *Phys Semicon Devices*, 3rd Edn John Wiley Sons, Inc NJ, 164 (2007) 682.

- 51 Tan T H & Goel A K, *Microw Opt Technol Lett*, 37 (2003) 366

- 52 Groeseneken G, Colinge J P, Maes H E, Alderman J C & Holt S, *IEEE Electron Device Lett*, 11 (1990) 329.